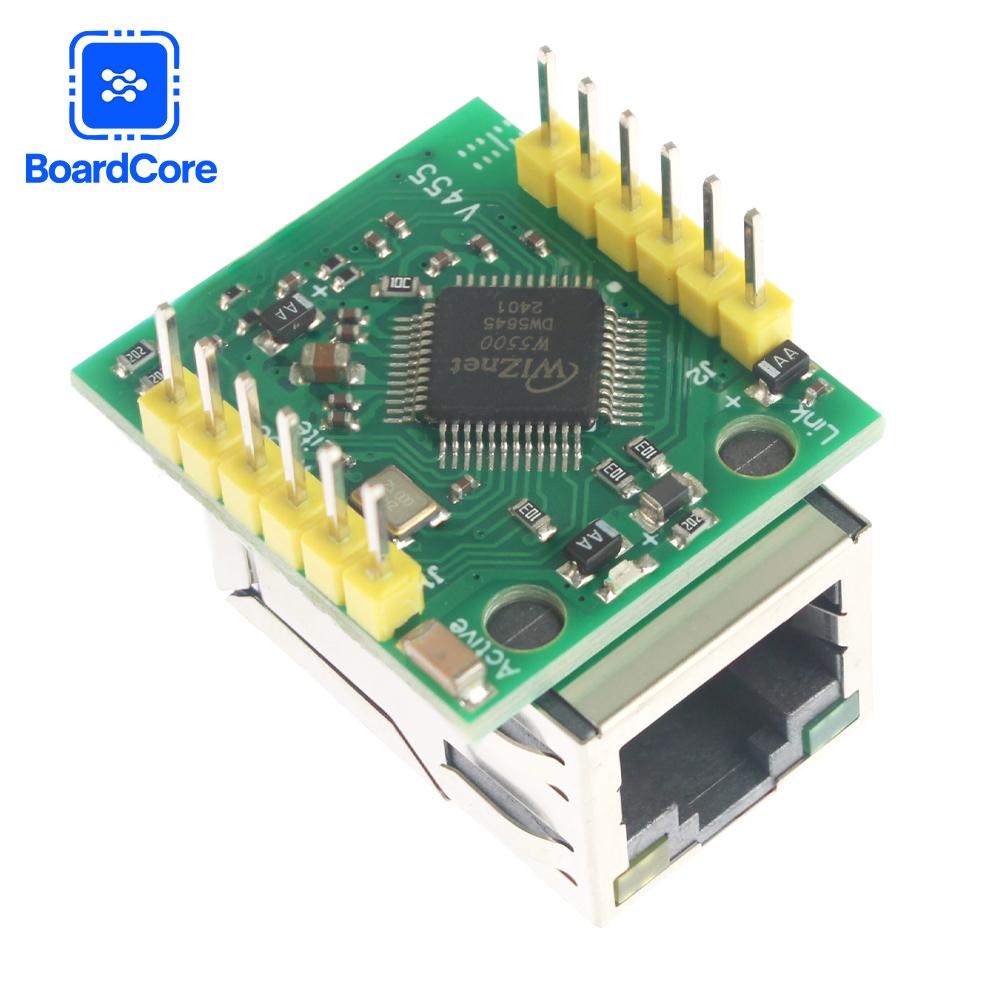

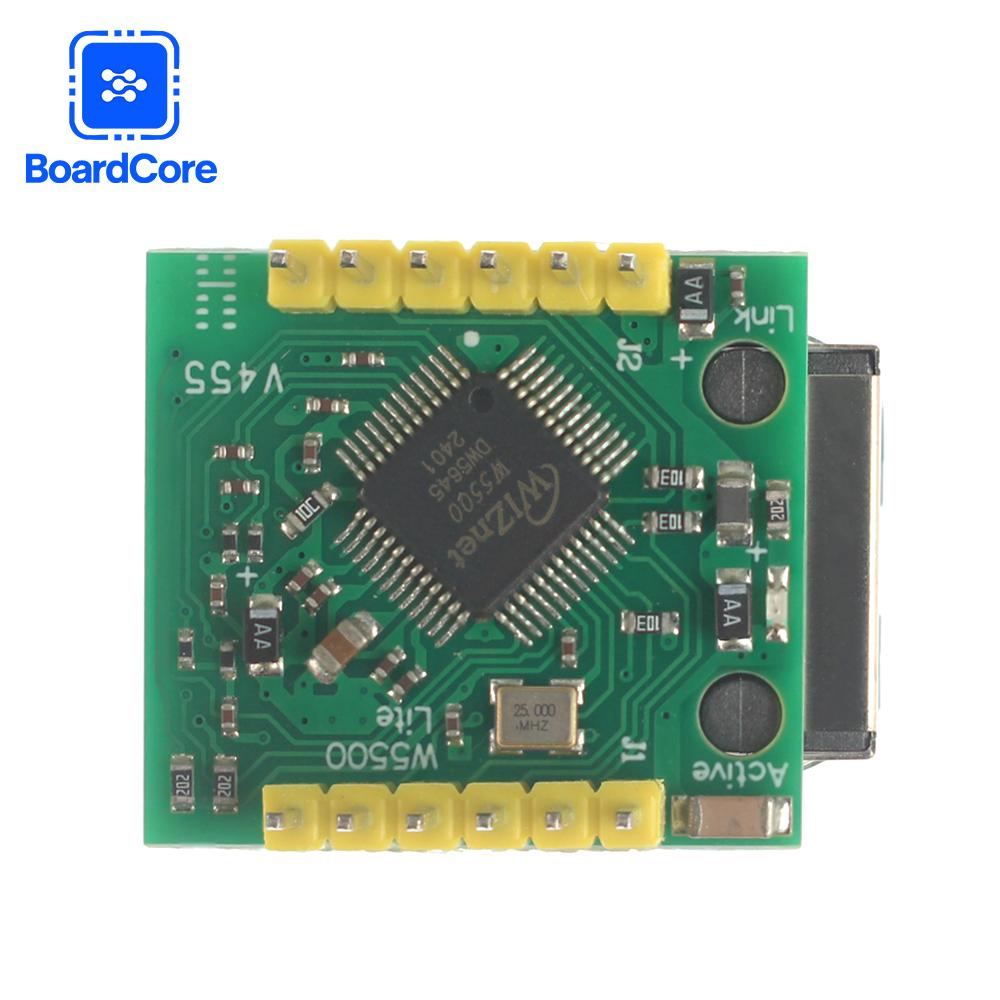

USR-ES1 Ethernet Module with W5500 Chip

Built-in Wiznet W5500 chip that implements TCP/IP stack in hardware (including TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE), integrated data link layer, physical layer, and 32KB on-chip RAM for efficient data buffering. Offloads network processing from the main MCU, allowing it to focus on application tasks—significantly improving system efficiency and reliability.

Operates like an external RAM device via a universal 80MHz high-speed SPI interface, enabling easy integration into various platforms. Features auto-negotiation and clear LED status indicators. Pin-compatible with WIZ820io.

Note: This module requires an external MCU and basic understanding of W5500 operation. STM32 example code provided.

🔹 Key Features:

80MHz high-speed SPI

Hardware TCP/IP stack — no deep protocol knowledge needed

Supports up to 8 simultaneous sockets

Protocols: TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE

Integrated MAC and PHY

Wake-on-LAN support

SPI modes 0–3 supported

32KB internal buffer

10/100M Ethernet PHY

Auto-negotiation (full/half duplex)

IP fragmentation not supported

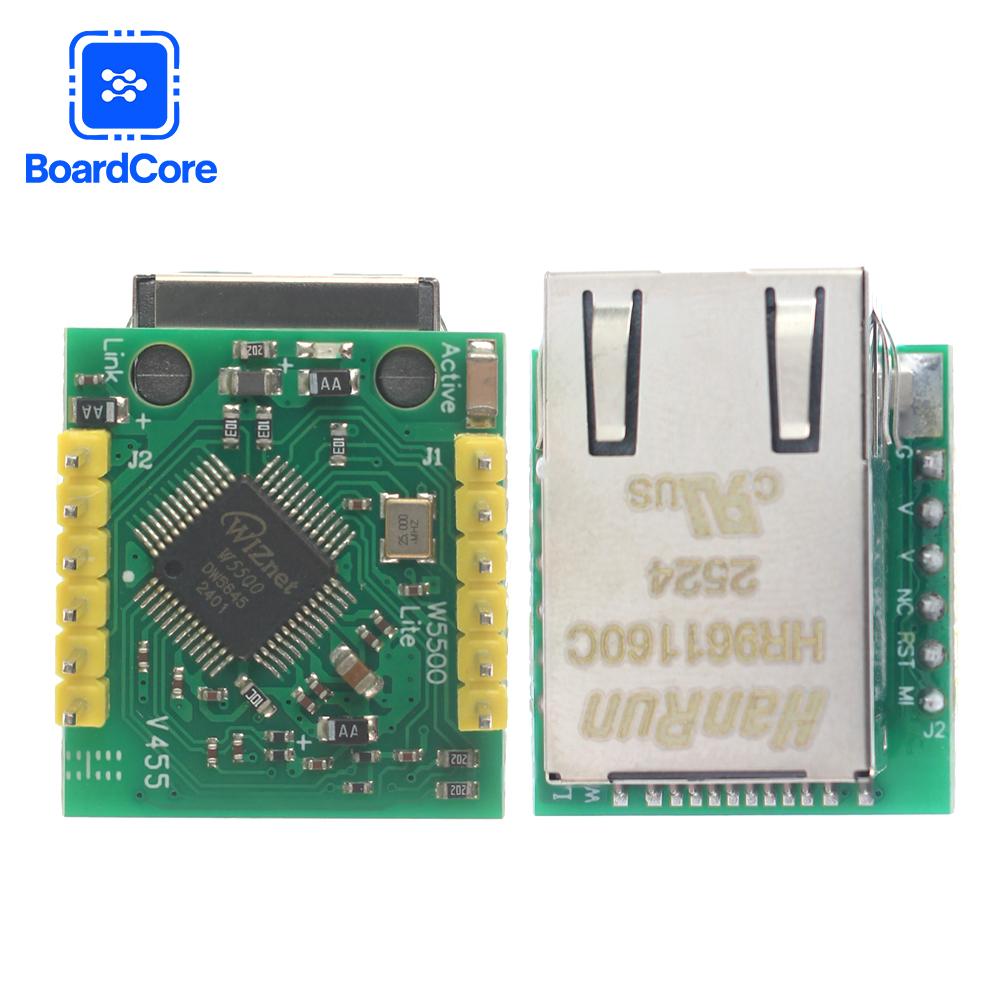

3.3V operation, 5V-tolerant I/Os

LED indicators: link, speed, duplex, activity

Compact pin-header design

🔹 Specifications:

Power: 3.3V (≥200mA)

Interface: 3.3V TTL SPI, 2× pin headers

PCB Size: 23×25 mm

Weight: 12g